메모리는 무엇인가???

메모리 소자는 SRAM, DRAM, NAND FLASH, Cloud storage로 크게 4가지로 나뉜다.

메모리 계층도

1) SRAM

- CPU가 빈번하게 사용하는 데이터를 저장한다. ( 캐시메모리 )

- 메모리 중에서 가장 빠르다.

- Cell 면적이 커서 용량이 낮다. → 높은 단가

2) DRAM

- 주 메모리의 역할

- 속도, 용량, 가격 : SRAM과 NAND flash 사이

3) NAND Flash

- 스토리지 메모리 (SSD, USB)의 역할

- 속도는 느리다.

- Cell 면적이 작아서 용량이 크다. → 낮은 단가

4) Cloud storage

- 인터넷 기반

- 속도가 느리고 보안에 취약하다.

- 비휘발성 메모리

로컬 스토리지에서 주 메모리로 내용을 전달하고, 주 메모리와 CPU가 내용을 주고 받는다.

1. SRAM(Static Random Access Memory) Cell 구조

SRAM 구조

1) 6개의 트랜지스터로 구성되어 있다.

- 데이터를 저장하는 latch TR 4개 (P1, P2, N1, N2) + WL 제어 접근 TR 2개 (N2, N4)

- 1bit(cell) → 2개의 CMOS 인버터가 서로 교차결합(cross coupled)되어 있다.

* 인버터 : IN (high) → OUT (low) 즉, 서로 반대의 값

- 상보적(0과 1) 데이터 형태로 저장한다.

2) Static : 전원이 공급되는 동안에는 데이터를 보존한다. >> 휘발성

3) RAM : X, Y 주소를 지정하면 어느 셀이든 임의 접근이 가능하다.

2. SRAM Cell의 동작 원리

1) 대기 상태 (데이터 보존)

- WL : OFF

- BL & /BL : 1 ( pre-charge )

- 만약 Q=0 & /Q=1 이면, P2 & N1 ON

- 만약 Q=1 & /Q=0 이면, P1 & N2 ON

- 전원(VDD & VSS) : ON (Latch 상태 유지)

2) 쓰기 (write)

- 이전 상태와 동일한 데이터인 경우

: 다른 변화 없이 그대로 상태 유지한다.

- 이전 상태와 반대인 데이터인 경우

: BL에서 1을 가하면, Q에 점점 전하가 쌓이면서 1이 된다. (Q : 0 → 1)

/Q는 P2와 N4를 통해 0으로 방전된다. (/Q : 1 → 0)

여기서 /Q이 방전되려면, N4>>P2 ( 구동능력)

3) 읽기 (read)

- WL : ON

- BL & /BL : 1(pre-charge) → Floating → 0 or 1

* Floating : 기생 캐패시턴스로 인한 전압 유지

- Q는 N1와 N2를 통해 0으로 방전된다. (Q : 1 → 0)

여기서 Q이 방전되려면, N1>>N2 ( 구동능력)

SRAM 트랜지스터의 구동 능력 : N1(N3) >> N2(N4) >> P2(P1)

DRAM이란???

1. DRAM (Dynamic Random Access Memory) Cell의 구조

DRAM 구조

- 1개의 트랜지스터(nMOS) + 1개의 캐패시터로 구성된다.

* 셀 트랜지스터 : 비트라인(통로) & 워드라인(스위치)

* 셀 캐패시터 : 데이터 저장

- Dynamic

: 캐패시터에 데이터를 저장하게 되면 시간이 지나면서 누설 전류에 의한 데이터 손실이 발생하는데,

이를 refresh을 통해 손실을 최소화시킨다.

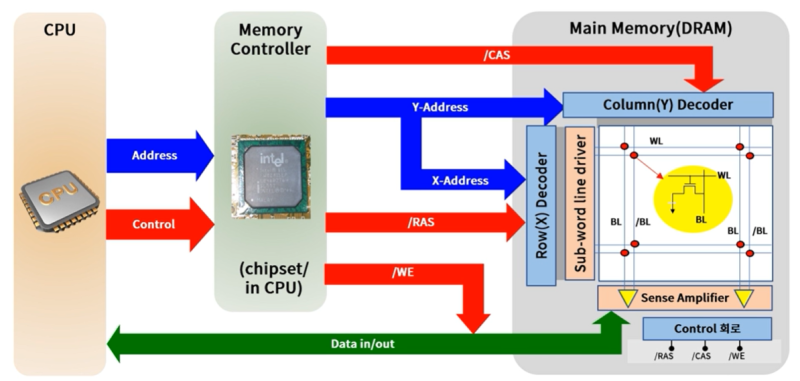

2. 시스템 내에서 DRAM 역할 및 DRAM chip 구성

- CPU에서 지정하는 DRAM 주소의 cell에 데이터를 쓰거나 읽는 동작을 한다.

( adress, data, control 명령에 의해 동작한다. )

- Cell array, Core, 주변회로로 구성된다.

3. DRAM 셀 동작원리

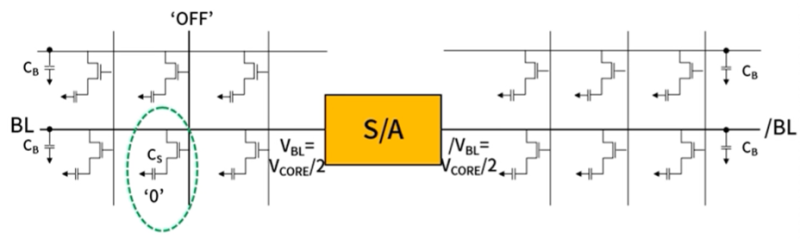

1) 대기 상태

- WL : OFF ( 캐패시터와 BL 격리)

- BL & /BL : Vcore / 2 (pre-charge) * Vcore =1

2) 쓰기 (write 1)

- WL : ON

- BL : Vcore

- 캐패시터 : 1 ( 충전 )

- /BL : 0 ( 방전 )

- 이후 다시 대시 상태 (1 저장)

3) 읽기 (write 1)

다음 과정에 의해 읽기 동작이 실행된다. 여기서 △VBL이 증가하면 안정적으로 동작할 수 있고 이를 위해 CS는 높이고 CB를 줄여야 한다.

Cell Capacitance ( CS )확보하기 위해서는 1) 면적을 늘리거나 2) 두께를 줄이거나 3) 유전체의 유전율을 증가시켜야 한다. 하지만 두께를 줄이게 되면 누설 전류가 증가하므로 면적을 늘리거나 유전체의 유전율을 증가시키는 방향을 고려하고 있다.

PN junction, sub-threshold, cell cap. dielectric 등으로 인해 누설 전류가 발생하고, 이로 인해 캐패시터의 전압이 감소하게 된다. 이는 주기적인 다시쓰기 동작인 refresh를 통해 줄일 수 있다.

최소 전압을 구분할 수 있는 시간인 retention time보다 더 빠르게 refresh time을 주기적으로 WL을 ON 시킨다.

4) Cell Capacitance 확보

앞서 언급했던 것처럼 안정적인 동작을 위해 △VBL을 증가시켜야하고 이를 위해선 CS는 높이고 CB를 줄여야 한다. 면적을 늘리거나 유전체의 유전율을 증가시키는 방향으로 CS는 높이고 있다.

DRAM이 미세화되면서 캐패시터는 점점 얇고 긴 모양으로 형성된다. 하지만 이러한 구조의 경우 넘어지거나 서로 부딪히는 경우가 발생하기 때문에 이를 방시하기 위해 mesh 구조를 사용한다.

유전체의 유전율을 증가시키면 bandgap이 감소하는 것을 볼 수 있는데 이는 누설 전류를 증가시키기 때문에 여러 유전체를 적층 구조로 쌓아 유전율을 좋으면서 누설전류는 낮은 지점을 찾는 것이 중요하다.

'주식 > 테마정리' 카테고리의 다른 글

| LG에너지 솔루션관련주 테마 (0) | 2021.11.25 |

|---|---|

| 이재명 정책주-디지털전환테마 (0) | 2021.11.24 |

| 반도체공정이해하기-반도체란 (0) | 2021.11.24 |

| NFT,P2E 게임관련주 정리 (0) | 2021.11.19 |

| 싸이월드테마 관련주 정리 (0) | 2021.11.19 |

댓글